ParityQC | The Quantum Architecture Company

ParityQC is the world’s only quantum architecture company. We develop blueprints and an operating system for highly scalable quantum computers, with applications ranging from solving optimization problems on NISQ devices to general-purpose, error-corrected quantum computing.

The ParityQC Architecture introduces a paradigm shift in the design and creation of quantum computers that are powerful, scalable and flexible, and our Parity Twine technology leads to the implementation of cornerstone quantum algorithms with record efficiency. Our co-development approach to hardware and software results in quantum chips and algorithms that fit together perfectly.

Real world problems

Quantum computers will be able to solve specific industry-relevant problems much faster compared to classical computers. One example is optimization problems, which are ubiquitous in the real world, from healthcare to finance, manufacturing to logistics. They are complex and intrinsically hard to solve.

Translation to Quantum Computers

Due to their complexity, real-world problems require a large number of qubits when encoding them on a quantum computer. In the standard approach, these problems are either encoded directly into the hardware or in gates between qubits. This results in complex chip layouts and large systems.

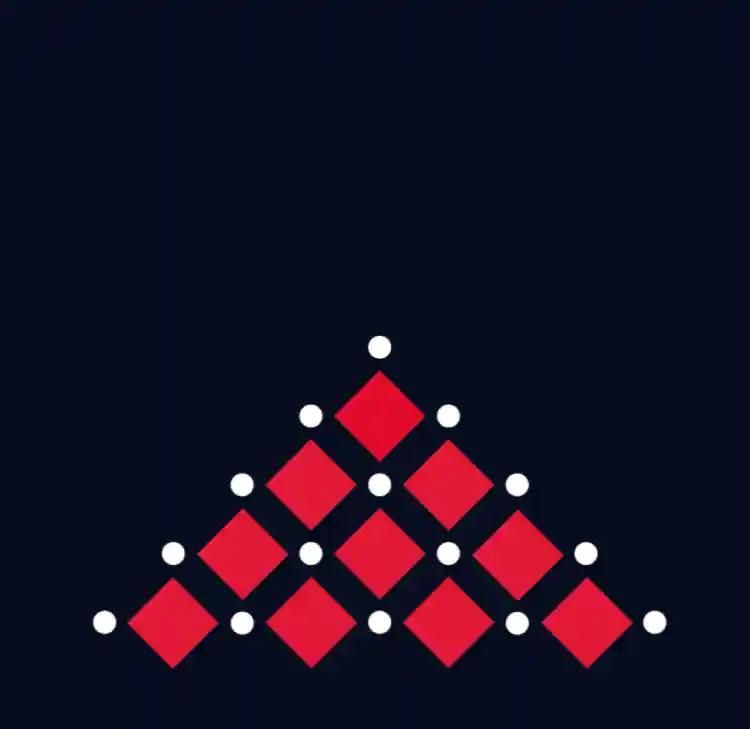

Reduced Complexity & Simplified Control

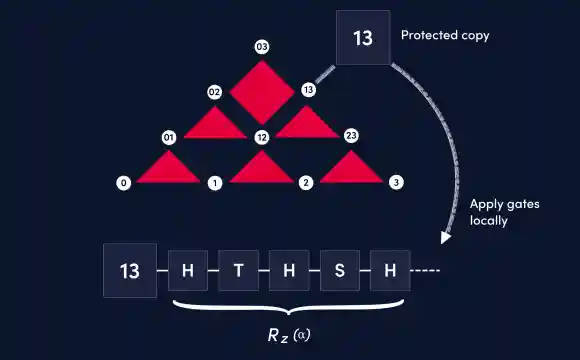

The ParityQC Architecture separates the problem from the hardware through a revolutionary and highly scalable design, in which the same chip can solve any type of problem. Its structure is simple and parallelizable, ensuring ease of scalability and full programmability, and it has an intrinsic error-correction potential. It provides benefits for every currently available 2D hardware platform and for both digital and analog methods.

A combined approach: hardware and software working in parity.

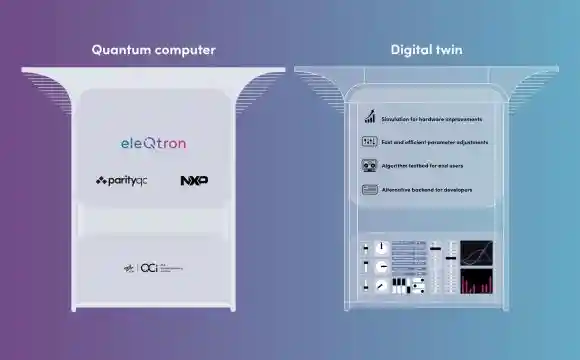

The key to a perfectly aligned quantum computer is the simultaneous development of hardware and software: this approach will ensure we achieve quantum advantage in the near term. By adopting our unique architecture together with ParityOS, hardware developers benefit from years of research in a complete package that offers a simple blueprint for quantum chips and an operating system that is easy to implement.

Performance with ParityOS

Solve real-world problems with simpler and smaller chips

ParityOS enables hardware developers and users to skip the spin-model representation and encode industry-relevant problems directly along with multi-variable correlations and side conditions. This introduces a new way of approaching industry-relevant problems with higher-order constrained binary optimization (HCBO).

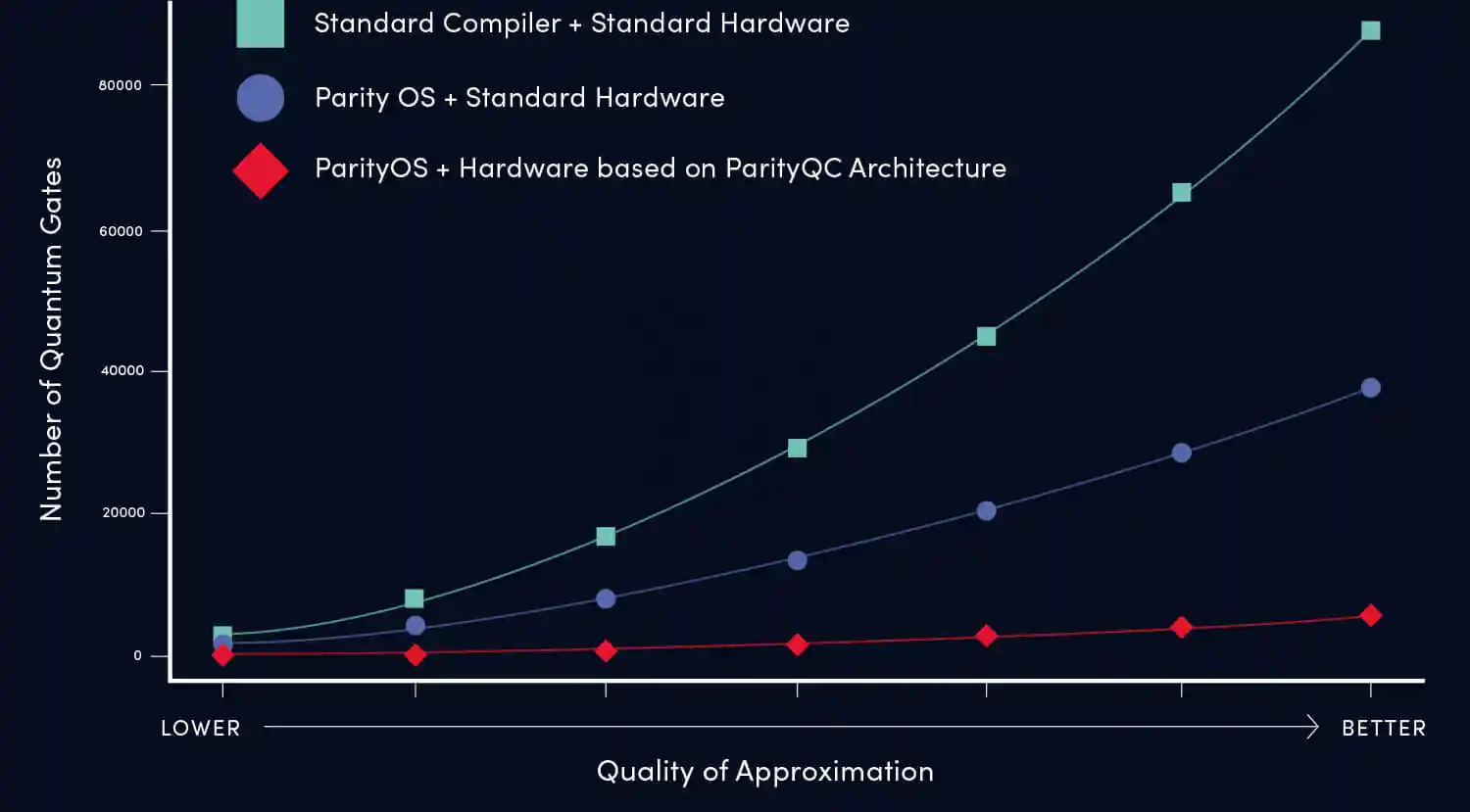

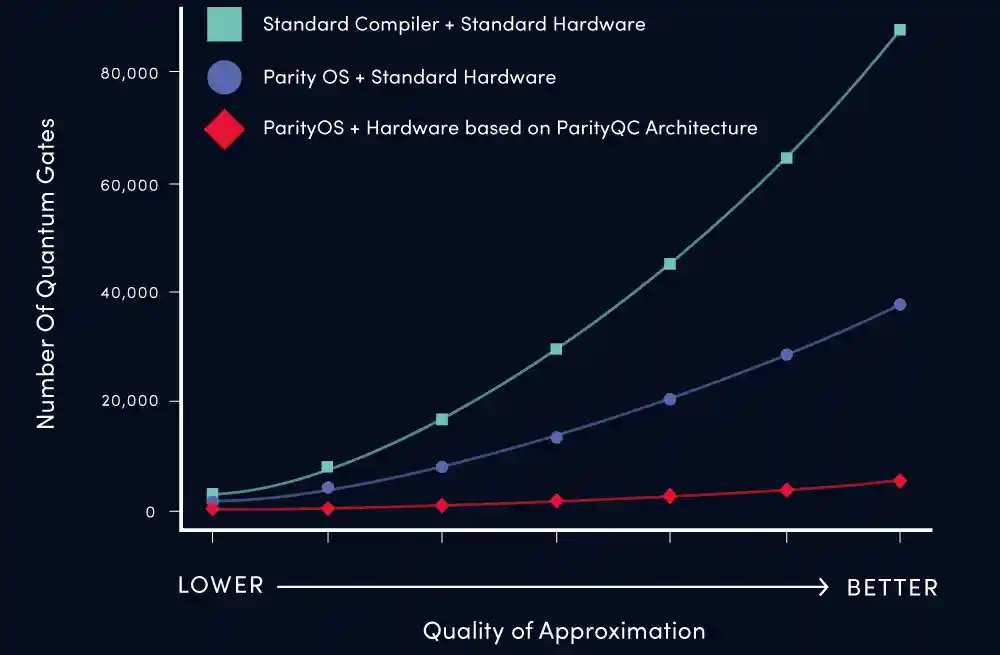

ParityOS and architecture performance in Quantum Chemistry: Groundstate calculation of LiH (lithium hydrid) molecule. For digital quantum computing, ParityOS substantially reduces the number of gates and total clock time compared to the standard gate model

Scalability at the core

Full parallelizability enables constant-depth algorithms: a new paradigm in quantum computing.

Software & Hardware In Parity

Trusted by

-

Parity Principles Parity Lectures – Working with quantum circuits through Parity Flow

-

News ParityQC joins PraktiQOM project, developing advanced quantum algorithms for semiconductor chip design

-

Papers Parallelizable, scalable, fault-tolerant multi-qubit Parity gates

-

Parity Principles Parity Principles – Quantum Error Correction with the Parity Code

-

News ParityQC awarded contract by DLR to integrate quantum computing for next-generation mobility solutions

-

News QSolid: quantum computer prototype is accessible through JUNIQ

-

News HPCQS: inauguration of Jade and Ruby Quantum Processors

-

News ParityQC is contributing to Europe’s first quantum computing standard

-

Awards ParityQC is a Semifinalist of XPRIZE Quantum Applications

-

Working at ParityQC Working in Quantum. Insights and behind-the-scenes with ParityQC’s Thorsten Strohmaier

-

News ParityQC delivers QSea I digital twin to DLR Quantum Computing Initiative

-

Parity Principles Parity Principles – An Architecture for Semiconductor Spin Qubits