stavros [at] ubinet . gr

I have a particular focus on spatial computing and FPGAs for compute intensive workloads at the Edge, as well exploring the RISC-V architecture including soft/hard processors and SoC for hardware acceleration. I work together with my supervisor Prof. Paris Kitsos.

My research experience also entails embedded systems and internet of things with multi-modal sensor technologies.

In the past, I have delved into wireless sensor networks and voice coding algorithms’ evaluation in mobile computing MSc Thesis.

As a radio amateur (SV2HZK) hobbyist I have a keen interest in satellite communication and weather data. Recently, I have built a weather satellite image receiver based on Raspberry Pi and an open- source project raspberry-noaa-v2. Furthermore, I also process earth observation data from EUMETSAT.

latest posts

selected publications

-

A Survey on RISC-V-Based Machine Learning Ecosystem

Information, 2023

In recent years, the advancements in specialized hardware architectures have supported the industry and the research community to address the computation power needed for more enhanced and compute intensive artificial intelligence (AI) algorithms and applications that have already reached a substantial growth, such as in natural language processing (NLP) and computer vision (CV). The developments of open-source hardware (OSH) and the contribution towards the creation of hardware-based accelerators with implication mainly in machine learning (ML), has also been significant. In particular, the reduced instruction-set computer-five (RISC-V) open standard architecture has been widely adopted by a community of researchers and commercial users, worldwide, in numerous openly available implementations. The selection through a plethora of RISC-V processor cores and the mix of architectures and configurations combined with the proliferation of ML software frameworks for ML workloads, is not trivial. In order to facilitate this process, this paper presents a survey focused on the assessment of the ecosystem that entails RISC-V based hardware for creating a classification of system-on-chip (SoC) and CPU cores, along with an inclusive arrangement of the latest released frameworks that have supported open hardware integration for ML applications. Moreover, part of this work is devoted to the challenges that are concerned, such as power efficiency and reliability, when designing and building application with OSH in the AI/ML domain. This study presents a quantitative taxonomy of RISC-V SoC and reveals the opportunities in future research in machine learning with RISC-V open-source hardware architectures.

-

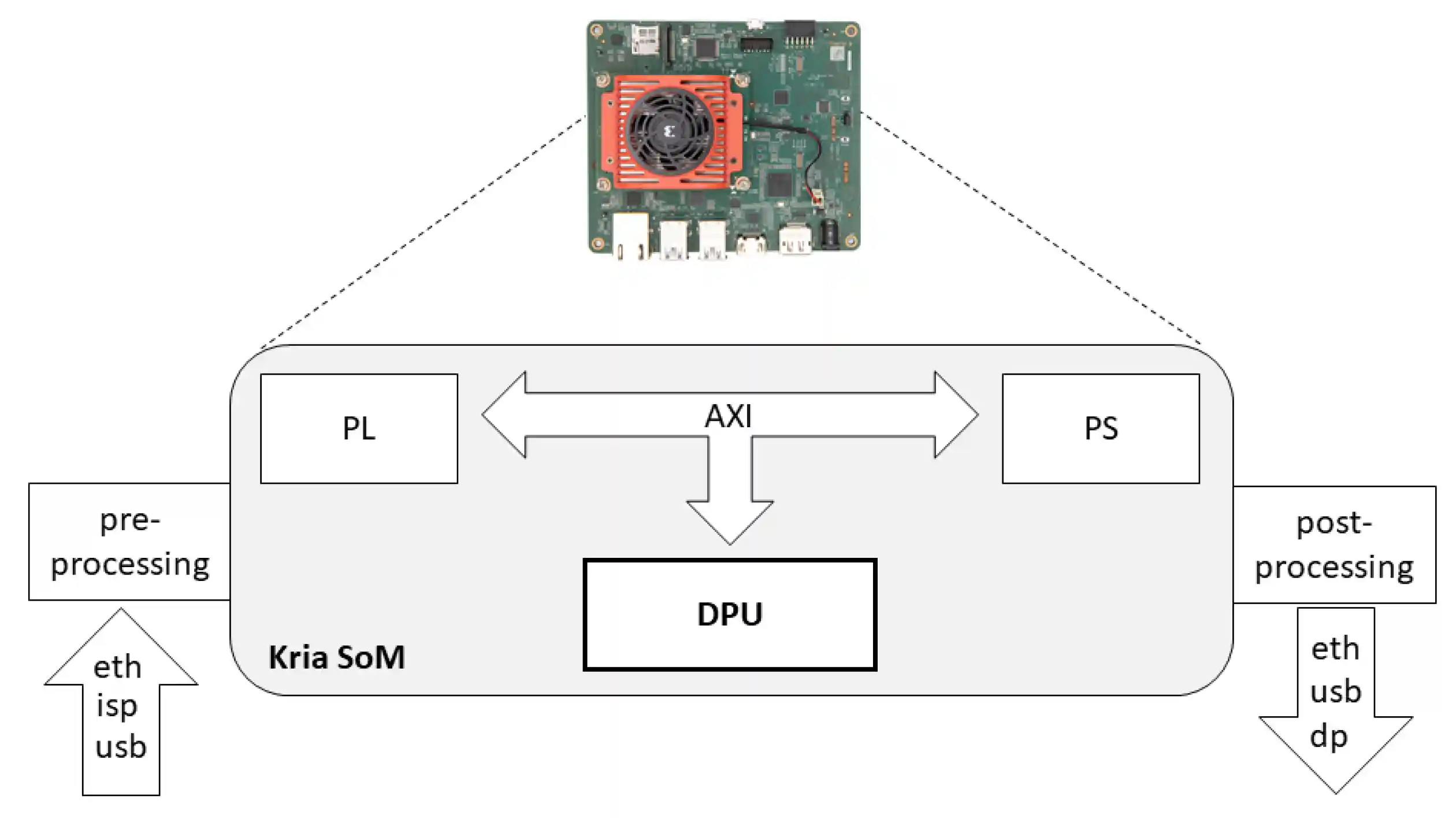

Efficient Edge-AI Application Deployment for FPGAs

Stavros Kalapothas , Georgios Flamis , and Paris Kitsos

Information, 2022

Field Programmable Gate Array (FPGA) accelerators have been widely adopted for artificial intelligence (AI) applications on edge devices (Edge-AI) utilizing Deep Neural Networks (DNN) architectures. FPGAs have gained their reputation due to the greater energy efficiency and high parallelism than microcontrollers (MCU) and graphical processing units (GPU), while they are easier to develop and more reconfigurable than the Application Specific Integrated Circuit (ASIC). The development and building of AI applications on resource constraint devices such as FPGAs remains a challenge, however, due to the co-design approach, which requires a valuable expertise in low-level hardware design and in software development. This paper explores the efficacy and the dynamic deployment of hardware accelerated applications on the Kria KV260 development platform based on the Xilinx Kria K26 system-on-module (SoM), which includes a Zynq multiprocessor system-on-chip (MPSoC). The platform supports the Python-based PYNQ framework and maintains a high level of versatility with the support of custom bitstreams (overlays). The demonstration proved the reconfigurabibilty and the overall ease of implementation with low-footprint machine learning (ML) algorithms.